it is amazing

on how many chips linux can run https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/arch

CPUs you probably have NEVER heared of 😀

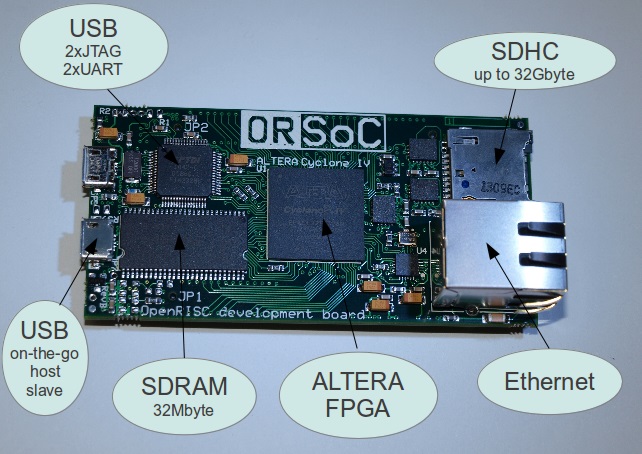

OpenRISC – Academic and non-commercial use

Being open source, OpenRISC has proved popular in academic and hobbyist circles. For example, Stefan Wallentowitz and his team at the Institute for Integrated Systems at the Technische Universität München have used OpenRISC in research into multicore architectures.[11] The Open Source Hardware User Group in the UK has on two occasions[12][13] run sessions on OpenRISC, while hobbyist Sven-Åke Andersson has written a comprehensive blog on OpenRISC for beginners,[14] which attracted the interest of EE Times.[15] Sebastian Macke has implemented jor1k, an OpenRISC 1000 emulator in JavaScript, running Linux with X Window System and Wayland support.[16]

https://en.wikipedia.org/wiki/OpenRISC

System on Chip

Links:

liked this article?

- only together we can create a truly free world

- plz support dwaves to keep it up & running!

- (yes the info on the internet is (mostly) free but beer is still not free (still have to work on that))

- really really hate advertisement

- contribute: whenever a solution was found, blog about it for others to find!

- talk about, recommend & link to this blog and articles

- thanks to all who contribute!